半導體為導電性介於導體與絕緣體之間的物質,包括矽、鍺等等,此類物質特性不若導體和絕緣體為絕對導電和絕對不導電,且具有較大的縫隙,以矽為例,該縫隙使矽有較大的雜質摻雜範圍,將矽注入雜質後,可以精確地調整導電性,因此矽可被用於製作重要的半導體電子元件—電晶體。

一、電晶體介紹

-

MOSFET

MOS全名是–金屬-氧化物-半導體場效電晶體(Metal Oxide Semiconductor Field Effect Transistor, MOSFET),構造如下圖,中間依序為金屬(紅色區塊)製成的閘極(Gate)、位於閘極下方相當薄的氧化物(黃色區塊)、最下方為半導體,因此得名為MOS。

電子自源極流入,通過閘極下方的電子通道後,從汲極流出。若閘極不加電壓,則電子無法通過,該元件呈現“關”的狀態;若閘極加正電壓,使電子可通過,則該元件呈現“開”的狀態。矽晶片上有數十億個電晶體,金屬導線將這數十億個電晶體的源極、汲極、閘極進行連結,使電子訊號可在之中流通進行運算。

在半導體製程常見的奈米製程其代表的是閘極長度,也就是製程線寬,又稱線寬。若閘極長度愈小,則電晶體愈小,若電晶體愈小則可以在更小的晶片中放入更多的電晶體,除了可提高處理器的運算效率外,可讓封裝後的積體電路體積愈小,體積的下降可以降低耗電量且迎合行動裝置輕薄化的趨勢。但當閘極長度縮小至20奈米以下時,面臨許多問題,例如:當閘極長度愈小表示源極和汲極之間的距離越小,閘極下方的氧化物也愈薄,此時很有可能因電子偷溜過閘極導致漏電;電子能否由源極流通至汲極是由閘極的電壓所控制,但是若閘極長度愈小則閘極下方的電子通道之間的接觸面積也將會愈小,閘極對電子通道的影響力愈小。

-

FinFET

美國加州大學胡正明、Tsu-Jae King-Liu、Jeffrey Bokor 等三位教授發明了鰭式場效電晶體(Fin Field Effect Transistor, FinFET),將2D 的MOSFET修改成為3D的FinFET,如下圖,透過將源極和汲極予以修正等等改善上述之問題,因構造和魚鰭相似,稱為鰭式(Fin)。

MOSFET與FinFET的差別為後者的源極和汲極加高成立體板狀結構,源極和汲極之間的通道也變成板狀,而閘極和通道之間的接觸面積也增加,使閘極能更有效地控制電流,控制電子從源極流通到汲極,也能讓FinFET在切換開關狀態時所消耗的電能減少,因此除了降低漏電發生的頻率也能更加省電。

10奈米以下的製程會面臨更險峻的困難,一顆原子的大小約為0.1奈米,若是10奈米則表示一條線上不到100顆原子,除了製作上的難度,且只要其中有一顆原子有缺陷,例如在製作過程中原子掉出或是有雜質,就會不知名的現象,進而影響產品的良率。

圖片來源:

科技新報 https://technews.tw/2015/09/15/what-is-finfet/

二、晶圓製程

晶圓是製造各式晶片的重要基礎,各式的電路圖成就晶片具備多樣的功能,例如:算術邏輯、記憶功能、數據傳輸、浮點運算等等。根據不同產品需求,工程師規劃晶片應具備的功能、各個功能分布在晶片的位置、所需的相關電子元件等等,進一步完成產品電路圖。待工程師完成產品電路圖後,將電路圖交由晶圓代工廠並委託生產。塊狀矽晶體經過長晶、切片、圓邊、研磨、蝕刻、去疵、拋光等步驟產出晶圓後,透過微影、蝕刻、清洗、雜質擴散、離子植入、薄膜沉積等程序將電路圖轉印至晶圓,完成後的晶圓進行最後的切割、測試、封裝等程序後成為動態記憶體、靜態記憶體、微處理器等等各式晶片。

-

晶圓製造

-

融化

將符合高純度要求的塊狀複晶矽放入石英坩鍋中,依據產品需求電性特質的不同加入特定的金屬物質,加熱至攝氏 1420 度的溶化溫度以上。此階段最重要的參數為坩鍋的位置與熱量的供應,融化複晶矽使用功率過高,會縮短石英坩鍋的壽命;功率過低則拉長融化的過程所需時間,進而影響產能。

-

形成矽晶柱(長晶)

當矽融漿的溫度穩定後,接著將晶種往上拉升,待直徑縮小到一定大小(約 6mm)後則維持此直徑並拉長 10-20cm,以消除晶種內的排差

(dislocation),此種零排差(dislocation-free)的控制主要目的是將排差侷限在頸部的成長。長完頸部後,慢慢地降低拉速與溫度,使頸部的直徑逐漸增加到所需的大小。利用拉速與溫度變化的調整維持固定的矽晶柱直徑,所以坩鍋必須不斷的上升來維持固定的液面高度,因此由坩鍋傳到矽晶柱及液面的輻射熱會逐漸增加,此輻射熱源使界面的溫度梯度逐漸變小,所以在晶棒成長階段的拉速必須逐漸地降低,以避免矽晶柱扭曲的現象產生。當晶體成長到固定(需要)的長度後,矽晶柱的直徑必須逐漸地縮小,直到與液面分開,避免因熱應力造成排差與滑移面現象。

- 矽晶柱品質的關鍵在於矽純度、拉晶速度和溫度控制等等,而矽晶柱直徑越大則技術難度越高、品質越難同時兼顧,因此直徑越大的矽晶圓廠其製程亦更加先進。

-

切片

矽晶柱完成後需再進行做裁切與檢測,先使用工業級鑽石模具進行加工,將晶柱磨成平滑圓柱體,並切除頭尾兩錐狀端,形成標準圓柱。再以內徑鋸進行裁切,內徑鋸其鋸片為環狀薄葉片,內徑邊緣鑲有鑽石顆粒,矽晶柱在切片前須預先黏貼石墨板,利於切片且可避免在最後切斷階段時鋸片離開矽晶柱造成破裂。切片晶圓的厚度、弓形度(bow)及撓屈度(warp)等特性皆為製程管制要點。影響晶圓品質的因素除了切割機台本身的穩定度與設計外,鋸片的張力狀況及鑽石銳利度的保持都有很大的影響。

-

圓邊

剛切好的晶圓片其邊緣皆為銳利的直角,由於其硬脆的材料特性,此角容易碎裂,除了影響晶圓強度,也會成為製程中污染微粒的來源,此外亦可防止後續製程中產生熱應力集中採用、鋪設光阻層與磊晶層的厚度與平坦度。電腦數值化機台自動修整切片晶圓的邊緣形狀與外徑尺寸。

-

研磨、蝕刻、去疵、拋光

研磨為去除切割或輪磨所造成的鋸痕沾附碎屑和污漬,使晶圓表面達到可進行拋光處理的平坦度;經前述加工製程後,表面因加工而形成一層損傷層(damaged layer),在拋光之前以化學溶劑蝕刻予以去除,再以離子純水沖洗吹乾; 利用噴砂法將晶圓上的瑕疵與缺陷趕到下半層,以利後續製程;邊緣拋光的主要目的在於降低微粒附著於晶圓的可能性,並使晶圓具備較佳的機械強度。機械與化學加工兩方法同時進行,將晶圓放置研磨機中,加工面壓貼在研磨墊摩擦,同時將具腐蝕性之化學溶劑滴入研磨機內作為研磨液之用,再以離子純水沖洗吹乾。

-

光罩處理

晶圓經過清洗後送至熱爐管內,在含氧的環境中以加熱氧化的方式在晶圓的表面形成一層二氧化矽層,厚約 1000A 到 2000A 的氮化矽層將以化學氣相沈積的方式沈積在剛剛形成的二氧化矽層上,才進行微影製程。

在晶圓表面上一層光阻(感光層),再將光罩上的圖案移轉到光阻上面。利用蝕刻技術,將部份未被光阻保護的氮化矽層去除,留下的就是所需要的線路圖部份。 接著以磷為離子源,對整片晶圓進行磷原子的植入,然後再把光阻劑去除。製程進行至此,我們已將構成積體電路所需的 電晶體及部份的字元線,依光罩所提供的設計圖案,依次的在晶圓上建立完成,接著進行金屬化製程,製作金屬導線,以便將各個電晶體與元件加以連接,而在每一道步驟加工完後都必須進行一些電性、物理特性量測,檢驗加工結果是否在規格內,如此重複步驟製作第一層、 第二層……的電路部份,最後所加工完成的產品會被送到電性測試區作電性量測。

極紫外光微影設備(EUV)

晶圓代工製程目前戰線主要專注在4奈米,根據Android Authority的報導指出,目前傳統微影技術已到達極限,欲發展至5奈米以下製程,波長更短的極紫外光微影設備(EUV)有其必要性。除了EUV外,在未來FinFET恐無法負荷技術升級,許多人認為「閘極全環場效電晶體」(Gate-all-around FET, GAAFET)最有可能會是最佳的解決方案,但欲實現5奈米晶片其所需光阻劑仍存在困難尚未克服,IC Knowledge總裁Scotten Jones表示:「在7奈米製程採用EUV的主要部份已經到位,但對於5奈米製程來說,光阻劑的缺陷仍然高出一個數量級」。

EUV微影與傳統的光罩全然不同,所有光罩材料皆為不透光,使用通稱極紫外線之極短波(13.5 nm)光線的微影技術,透過高能量、波長短的光源將電路圖案投射至晶圓上。但一台EUV微影機臺價格不斐,一臺高達1.1億美元(約新台幣33.56億元),除了昂貴以外,耗電也是其令人卻步原因之一,身為世界第二大記憶體製造商的SK海力士曾在2009的EUV Symposium表示:「EUV的能源轉換效率僅約0.02%」。也就是說目前最先進的EUV機臺其光源功率能輸出250瓦,需輸入0.125萬瓩的電力,此耗電量為傳統氬氟雷射的10倍不只,而晶圓生產速度可達每小時125片,但僅為台積電、Intel等大客戶所提出之量產最低要求。EUV這樣的極紫外光非常容易被吸收,甚至空氣也不透光,因此整個生產機房環境必須為真空,此外極紫外光也無法以玻璃透鏡折射,須經由矽與鉬製作特殊鍍膜反射鏡來修正光的前進方向,且每一次反射仍會損失3成能量,而一台EUV機台得經過十幾面反射鏡,光從光源一路導到晶圓最後大概只剩下不到2%的光線,這也是EUV機臺如此耗電的主要原因之一。此外,冷卻系統也是EUV機臺耗電的主因之一,冷卻系統除了造成大量耗電問題外,也提高了提升功率的困難性。

法人表示18年將會是EUV技術進入量產的關鍵時機,台積電第二代7奈米製程和5奈米製程皆採用EUV技術進行生產,預估第二代7奈米製程將在19年量產,5奈米製程於19年第一季進行風險試產、20年正式進入量產;Samsung於18年將推出採用EUV技術的7奈米晶圓代工服務;Intel於10奈米製程後才會逐步使用EUV技術,目前已確定EUV微影將成為半導體微影技術主流。

-

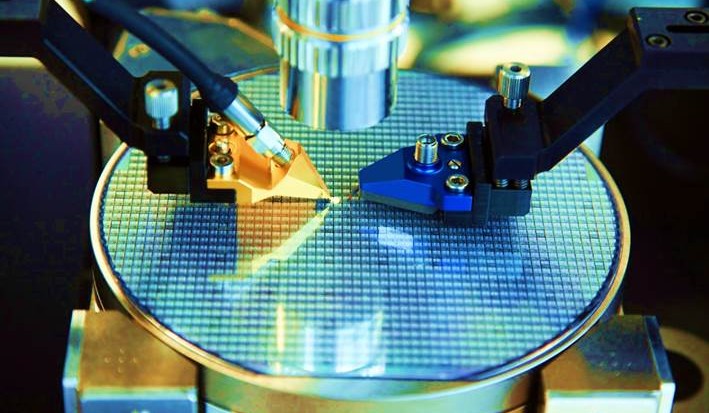

晶圓針測

目的是針對晶片作電性功能上的測試,使 IC在進入封裝前,先過濾出電性功能不良的晶片,以避免不良品增加製造成本。半導體製程中,針測製程只要換上不同的測試配件,便可與測試製程共用相同的測試機台。一般測試廠為了提高測試機台的使用率,除了提供最終測試的服務外,亦接受晶片測試的訂單。

- 晶圓針測並作產品分類

晶圓針測的主要目的是測試晶圓中每一顆晶粒的電氣特性,線路的連接,檢查其是否為不良品,若為不良品,則點上一點紅墨水,作為識別之用。另一目的是測試產品的良率,依良率的高低來判斷晶圓製造的過程是否有誤。良品率高表示晶圓製造過程一切正常,若良品率過低,則表示在晶圓製造的過程中,有某些步驟出現問題,必須儘快通知工程師檢查。

- 雷射修補

雷射修補的目的是修補那些尚可被修復的不良品(有設計備份電路在其中者),提高產品的良品率。當晶圓針測完成後,擁有備份電路的產品會與其在晶圓針測時所產生的測試結果資料一同送往雷射修補機中,這些資料包括不良品的位置,線路的配置等。雷射修補機的控制電腦可依這些資料,嘗試將晶圓中的不良品修復。

- 加溫烘烤

加溫烘烤是針測流程中的最後一項作業,加溫烘烤的目的有「將點在晶粒上的紅墨水烤乾」與「清理晶圓表面。經過加溫烘烤的產品,只要有需求便可以出貨」。

-

封裝與測試:

8吋晶圓廠代表該廠其生產出的矽晶柱切成薄片後的晶圓直徑為8吋,此尺寸決定後續裁切出的晶片數量多寡。而晶圓上呈現一格一格小方格,依小方格再切割成一片片的裸晶(Die),待裸晶封裝後才稱作晶片。這些小方格內可放入電晶體,因此電晶體體積愈小,晶圓便可放置越多的電晶體,晶片可擁有越多越複雜的功能。由於裸晶體積相當小又薄、十分容易被刮傷,故封裝廠會將裸晶安裝在導線架上、在外面封裝上絕緣的塑膠體或陶瓷外殼,剪下來印上委託製造公司的標誌,最後進行測試,進行晶片結構及功能的確認、將不良品挑出。

- 封裝(分割-黏晶-加外接引腳及包覆):

提供一個引接的介面,電路內部電性訊號可購過引腳(封裝材料連接至系統,且避免電路受到機械性刮傷或高溫破壞,利用塑膠或陶瓷包裝晶粒與配線形成積體電路(Integrated Circuit, IC),最後積體電路周圍會向外拉出腳架(Pin),稱之為打線,用於連接外界電路板。

- 測試:

測試包裝後晶粒其電氣特性,測試消耗功率、速度、電壓容忍度等等,測試後的IC依照電氣特性分別置入不同的Bin之中,此過程又稱作Bin Splits。最後應客戶需求之規格於相對應的Bin中取出部分IC進行特殊測試和燒機,測試完成後即為成品,可貼上規格標籤,待包裝後即可交予顧客,不合者則降級或淘汰。